向集成一万亿晶体管的芯片迈进

日期:2022-12-11 21:39:21 / 人气:267

最近,英特尔副总裁兼技术开发负责人Ann Kelleher在IEDM 2022的相关新闻发布会上表示,英特尔正在按照设定的里程碑前进。根据这些里程碑,英特尔正走在正确的道路上,处于领先地位。

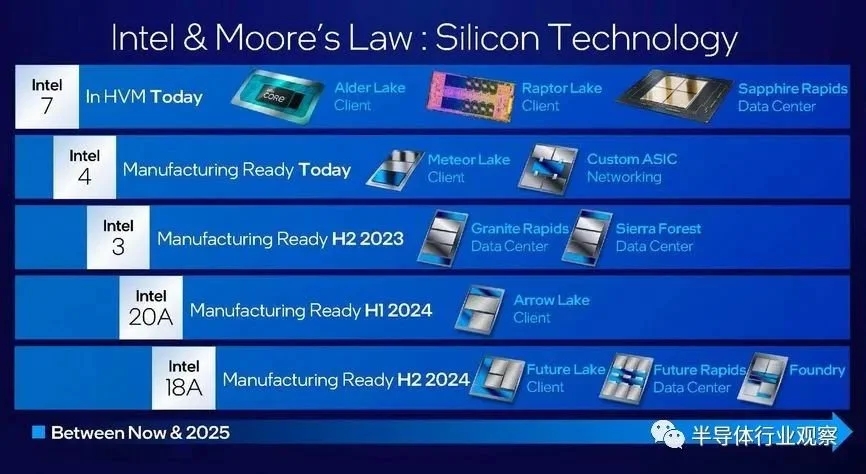

Ann Kelleher进一步指出,该公司已经准备好进入英特尔4工艺,并在2023年下半年切换到英特尔3工艺。虽然专有名词Intel 7可能与芯片的实际生产关系不大,但Ann Kelleher表示,该公司的团队正在努力推动制造工艺的发展,以恢复英特尔昔日的辉煌。她还表示,R&D的预算是由高层承诺保证的,不会受到公司削减成本的影响。在她的介绍中,她还重申了英特尔到2030年开发出超过一万亿晶体管的处理器的承诺。

这种说辞的原因在于,英特尔在IEDM 2022上发表了几篇论文,涉及该公司在2D材料晶体管、3D集成和存储技术方面的进展。在此,我们将其整合,为读者提供晚餐。

一种将硅片堆叠连接密度提高10倍的方法

熟悉芯片行业的读者应该知道,在过去的岁月里,晶体管密度的增长速度大致符合摩尔定律,但今天的芯片经济并没有以同样的速度改善——随着我们向更密集的节点转移,每个晶体管的价格都在上涨。此外,一些芯片组件(如模拟和缓存)的可扩展性很差,这使得事情变得更加复杂。

因此,业界正集体转向基于小芯片的高性能芯片设计。

然而,任何基于小芯片的设计的主要目标都是保持单芯片单片处理器的内部数据路径的功耗和性能(延迟、带宽)的最佳属性,同时利用基于小芯片的方法的经济优势,例如能够使用尖端技术来制造具有更高产量的小芯片,并使用更老、更便宜的节点来实现其他功能,而密度提高较少。

因此,半导体霸权的战场正在从晶体管的速度转向互连的性能,硅内插器(EMIB)和混合键合技术等新技术成为提高经济性的前沿。

然而,这些方法仍然导致在性能、功耗和成本方面不可避免的折衷。在本次IEDM上,英特尔带来了题为“在英特尔处理器上实现下一代3d异构集成架构”的演讲。其中,他们新推出的“准单片芯片”(QMC) 3D封装技术就是为解决这一问题而阐述的。

顾名思义,英特尔的QMC旨在提供与单个芯片内置互连几乎相同的功能。

众所周知,用于堆叠和电连接形成小芯片的管芯的技术可以大致分为两种类型:微凸块连接和混合键合。混合键合是一种理论上可以缩短连接距离的技术,换句话说,就是增加连接密度(面密度)。英特尔推出的QMC是一种新的混合粘合技术。

从相关报道可以看出,杂化键合有三个优点。第一是可以实现超精细的间距和超小的触点尺寸,因此可以实现超高的I/O数;其次,用介质材料键合代替底部填充,可以节省填充成本;再次,混合键合几乎没有厚度,未来3D封装技术的发展需要堆叠很多层芯片,所以混合键合可以大大降低整体厚度。

这也是英特尔做出这个选择的原因。

根据英特尔的最新论文,新方案的间距小于3微米。与他们去年在IEDM提交的研究相比,其能效和性能密度提高了10倍。在之前的论文中,他们介绍了一种间距为10微米的方法,但根据新论文的发表,它实现了10倍的改进。换句话说,英特尔找到了在短短几年内实现100倍提升的方法,这表明该公司在混合粘合方面的工作正在快速加速。值得一提的是,QMC还可以允许多个小芯片相互垂直堆叠。

作者:高德娱乐平台官网

新闻资讯 News

- “德云社隐形富豪,郭德纲50亿资...12-04

- 央视《小满生活》被批,生活剧要...12-04

- “休为刘诗诗新剧打call,贾斯汀...12-04

- “马伊俐带女儿出游,马被曝光,...12-04